Radiance Instruments TMW017G SMOKE GATEWAY User Manual TMW017G WIFI MODULE SPECIFICATION

Radiance Instruments Ltd. SMOKE GATEWAY TMW017G WIFI MODULE SPECIFICATION

Contents

- 1. TMW017G_Manual_r2

- 2. TMW017G_WIFI MODULE SPECIFICATION

TMW017G_WIFI MODULE SPECIFICATION

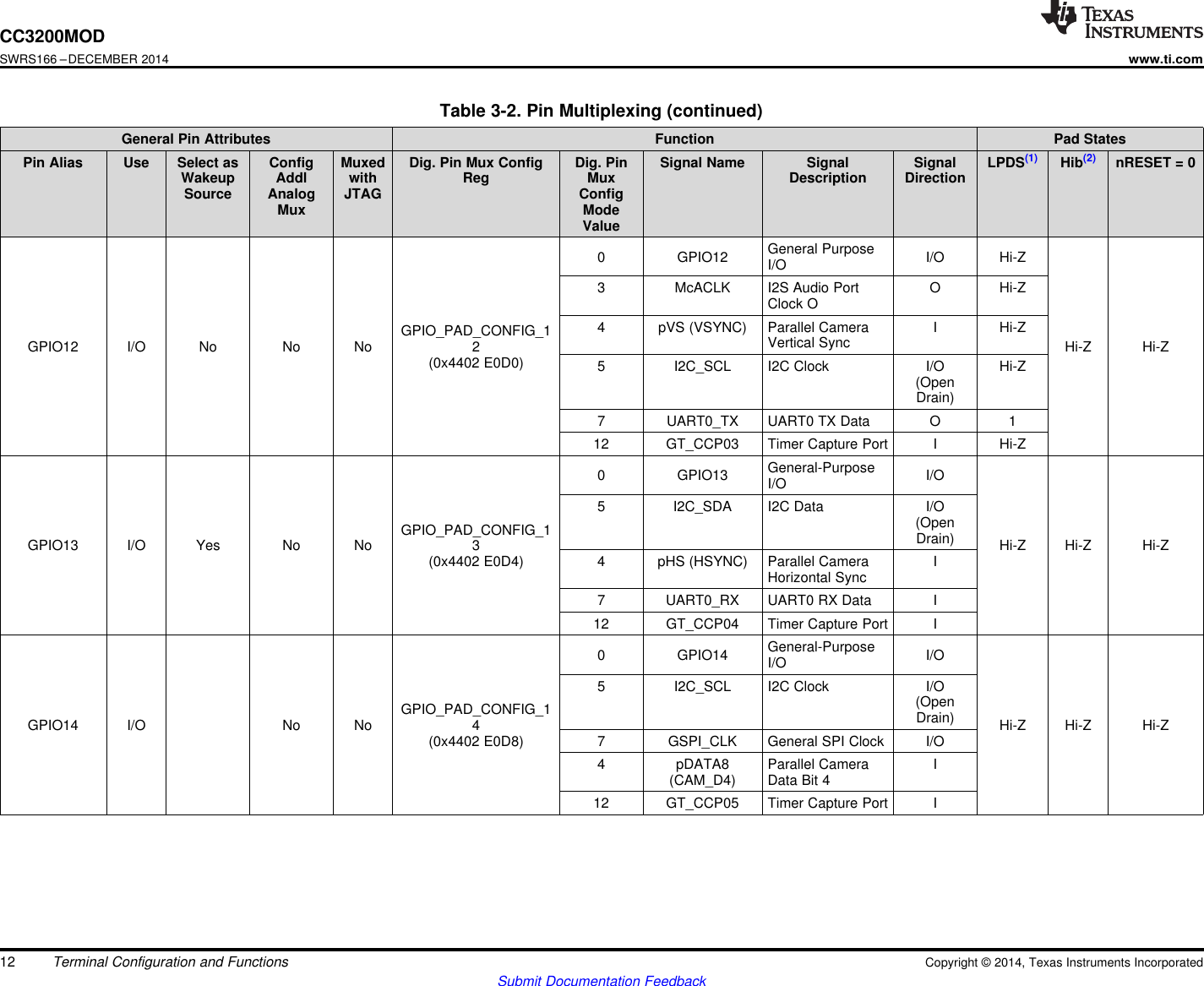

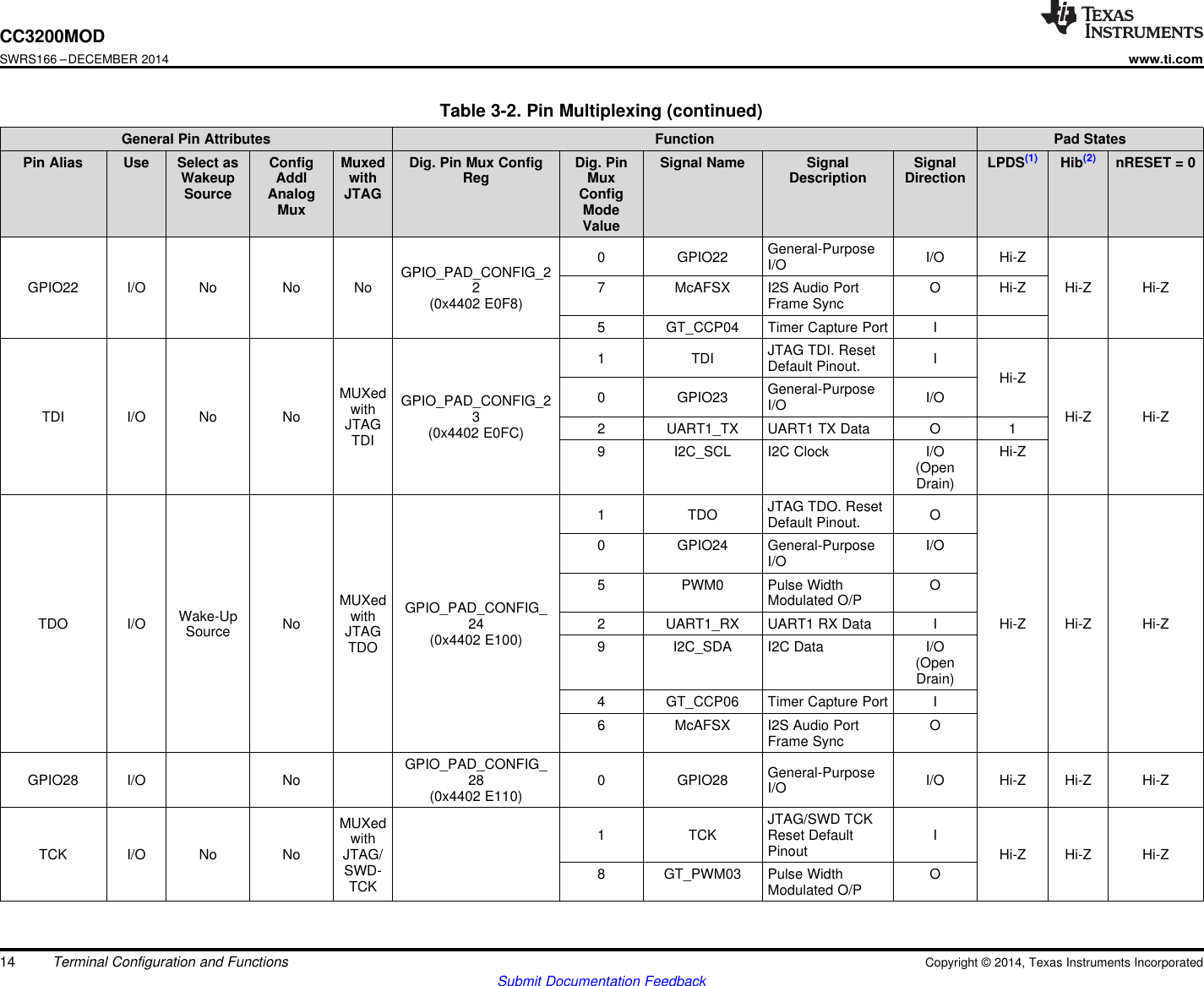

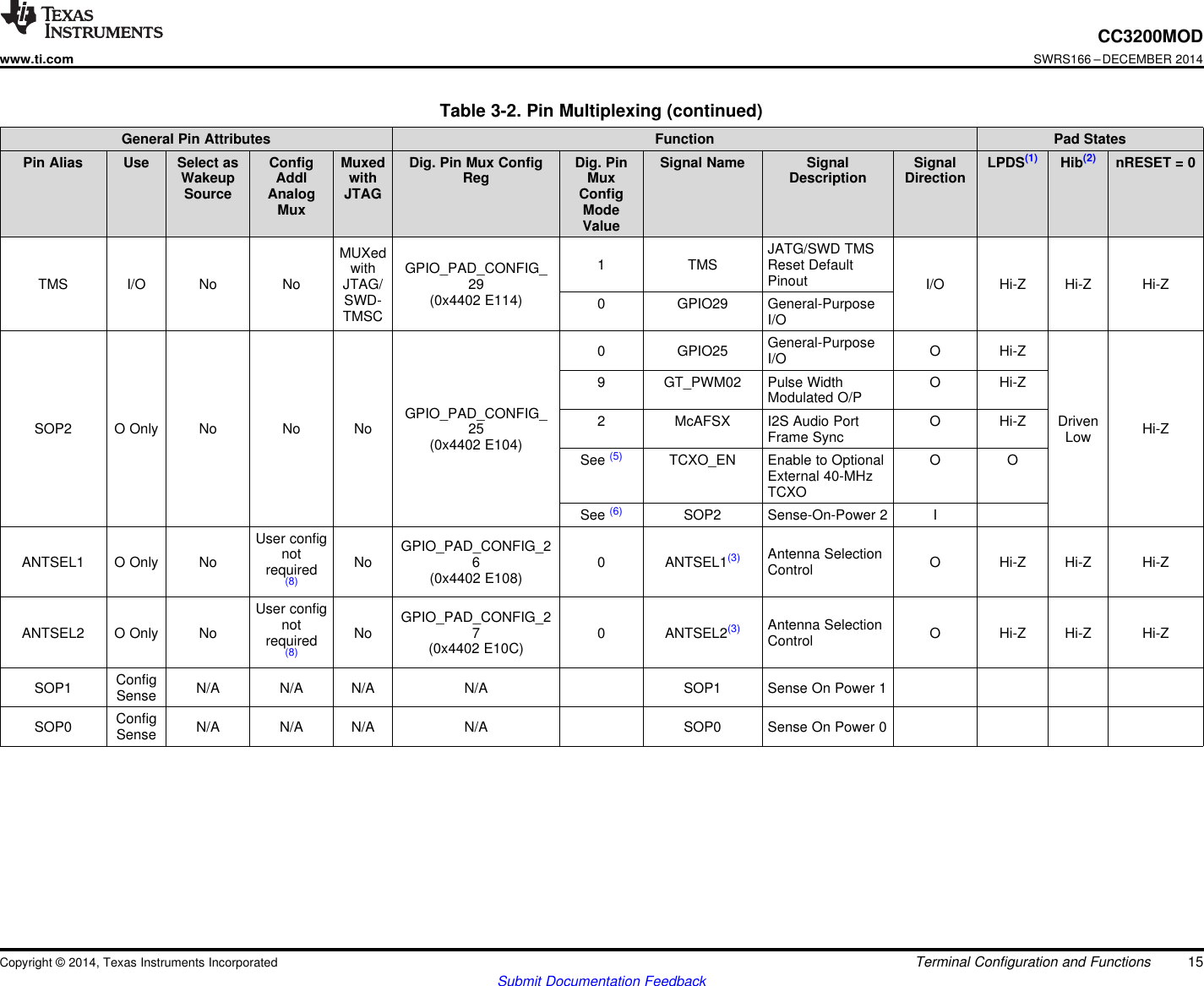

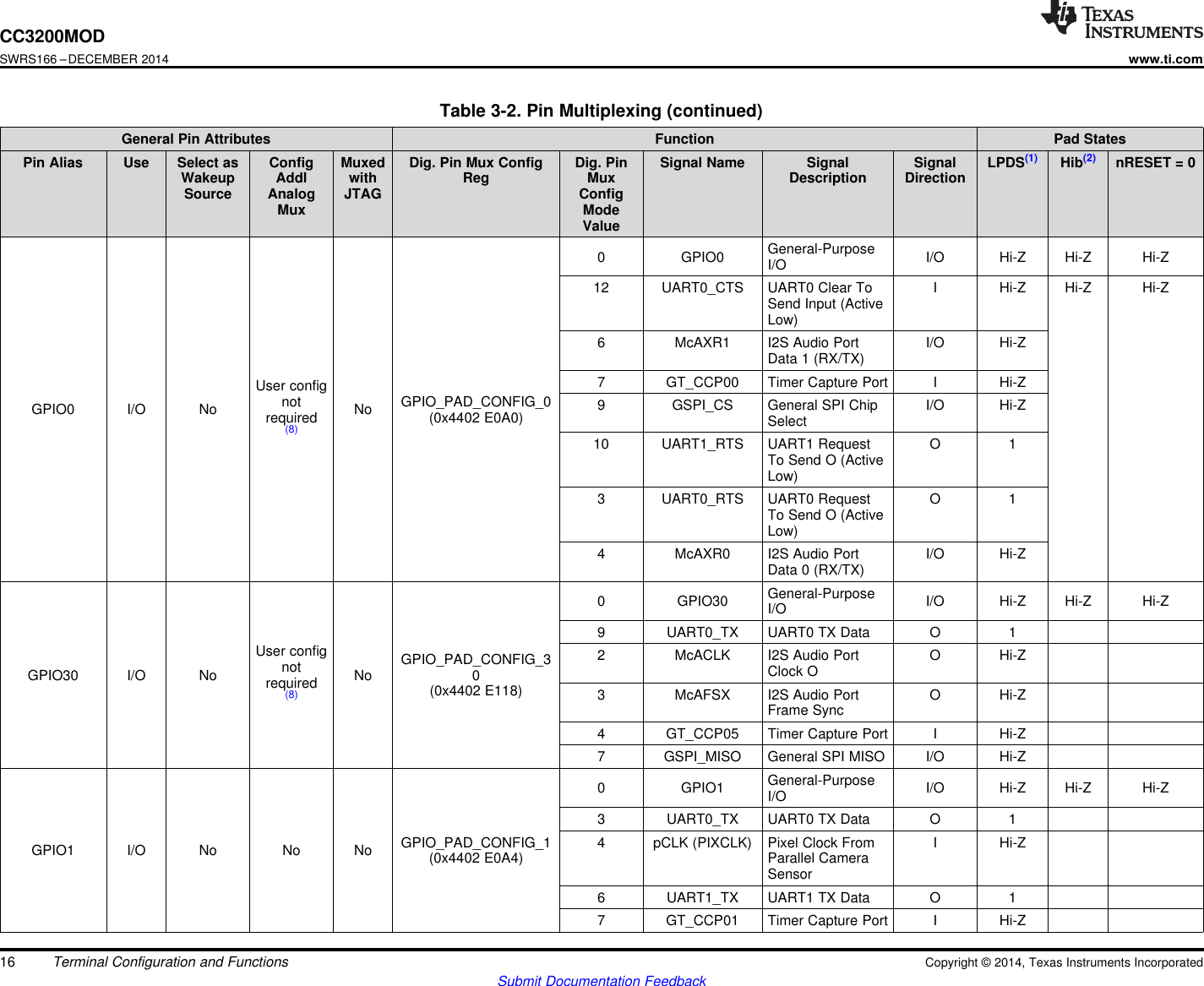

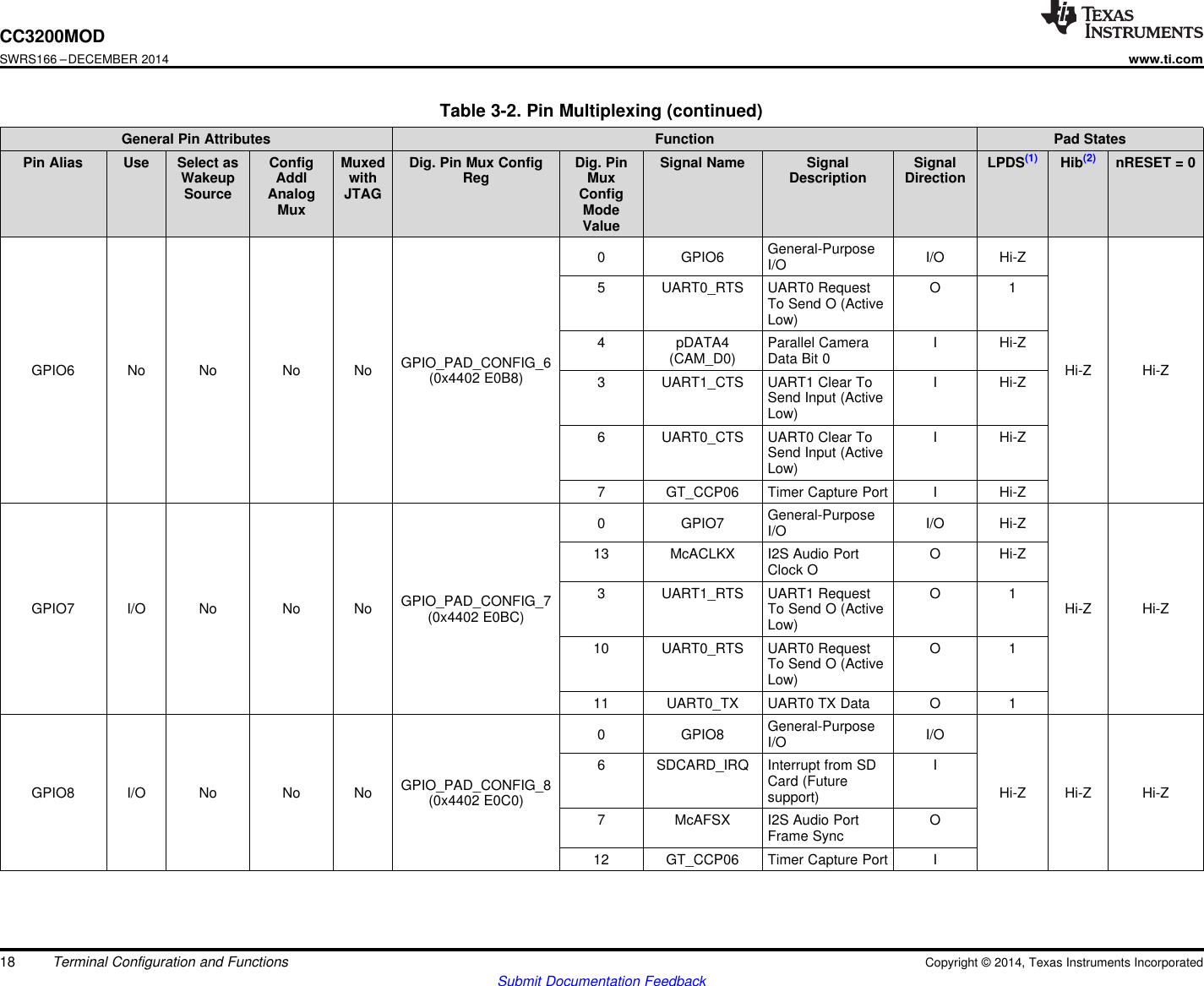

![CC3200MODwww.ti.comSWRS166 –DECEMBER 2014Table 3-2. Pin Multiplexing (continued)General Pin Attributes Function Pad StatesPin Alias Use Select as Config Muxed Dig. Pin Mux Config Dig. Pin Signal Name Signal Signal LPDS(1) Hib(2) nRESET = 0Wakeup Addl with Reg Mux Description DirectionSource Analog JTAG ConfigMux ModeValueGeneral-Purpose0 GPIO9 I/OI/O3 GT_PWM05 Pulse Width OModulated O/PGPIO_PAD_CONFIG_9GPIO9 I/O No No No 6 SDCARD_ SD Cad Data I/O Hi-Z Hi-Z Hi-Z(0x4402 E0C4) DATA07 McAXR0 I2S Audio Port I/OData (Rx/Tx)12 GT_CCP00 Timer Capture Port I(1) LPDS mode: The state of unused GPIOs in LPDS is input with 500-kΩpulldown. For all used GPIOs , the user can enable internal pulls, which would hold them in a valid state.(2) Hibernate mode: The CC3200 device leaves the digital pins in a Hi-Z state without any internal pulls when the device enters hibernate state. This can cause glitches on output lines unlessheld at valid levels by external resistors.(3) To minimize leakage in some serial flash vendors during LPDS, TI recommends the user application always enable internal weak pulldowns on FLASH_SPI_DATA and FLASH_SPI_CLKpins.(4) This pin has dual functions: as a SOP[2] (device operation mode), and as an external TCXO enable. As a TXCO enable, the pin is an output on power up and driven logic high. Duringhibernate low-power mode, the pin is in a high impedance state but pulled down for SOP mode to disable TCXO. Because of SOP functionality, the pin must be used as output only.(5) For details on proper use, see Drive Strength and Reset States for Analog-Digital Multiplexed Pins.(6) This pin is one of three that must have a passive pullup or pulldown resistor on board to configure the chip hardware power-up mode. For this reason, the pin must be output only whenused for digital functions.(7) This pin is reserved for WLAN antenna selection, controlling an external RF switch that multiplexes the RF pin of the CC3200 module between two antennas. These pins should not beused for other functionalities in general.(8) Device firmware automatically enables the digital path during ROM boot.(9) This pin is shared by the ADC inputs and digital I/O pad cells. Important: The ADC inputs are tolerant up to 1.8 V. On the other hand, the digital pads can tolerate up to 3.6 V. Hence, caremust be taken to prevent accidental damage to the ADC inputs. TI recommends that the output buffer(s) of the digital I/Os corresponding to the desired ADC channel be disabled first (thatis, converted to high-impedance state), and thereafter the respective pass switches (S7, S8, S9, S10) should be enabled (see Drive Strength and Reset States for Analog-DigitalMultiplexed Pins).(10) Requires user configuration to enable the ADC channel analog switch. (The switch is off by default.) The digital I/O is always connected and must be made Hi-Z before enabling the ADCswitch.3.4 Recommended Pin Multiplexing ConfigurationsTable 3-3 lists the recommended pin multiplexing configurations.Copyright © 2014, Texas Instruments Incorporated Terminal Configuration and Functions 19Submit Documentation Feedback](https://usermanual.wiki/Radiance-Instruments/TMW017G.TMW017G-WIFI-MODULE-SPECIFICATION/User-Guide-3512429-Page-19.png)

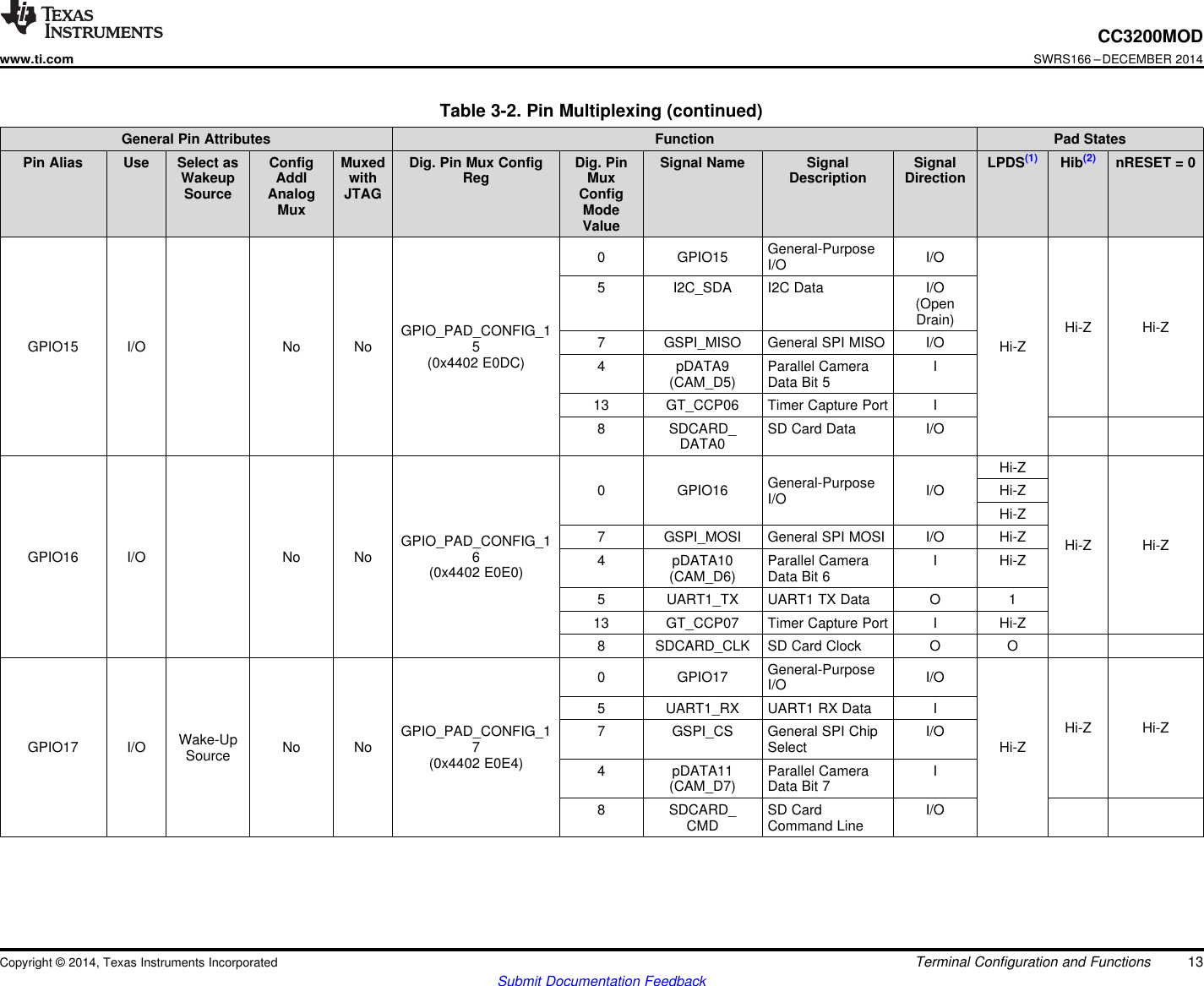

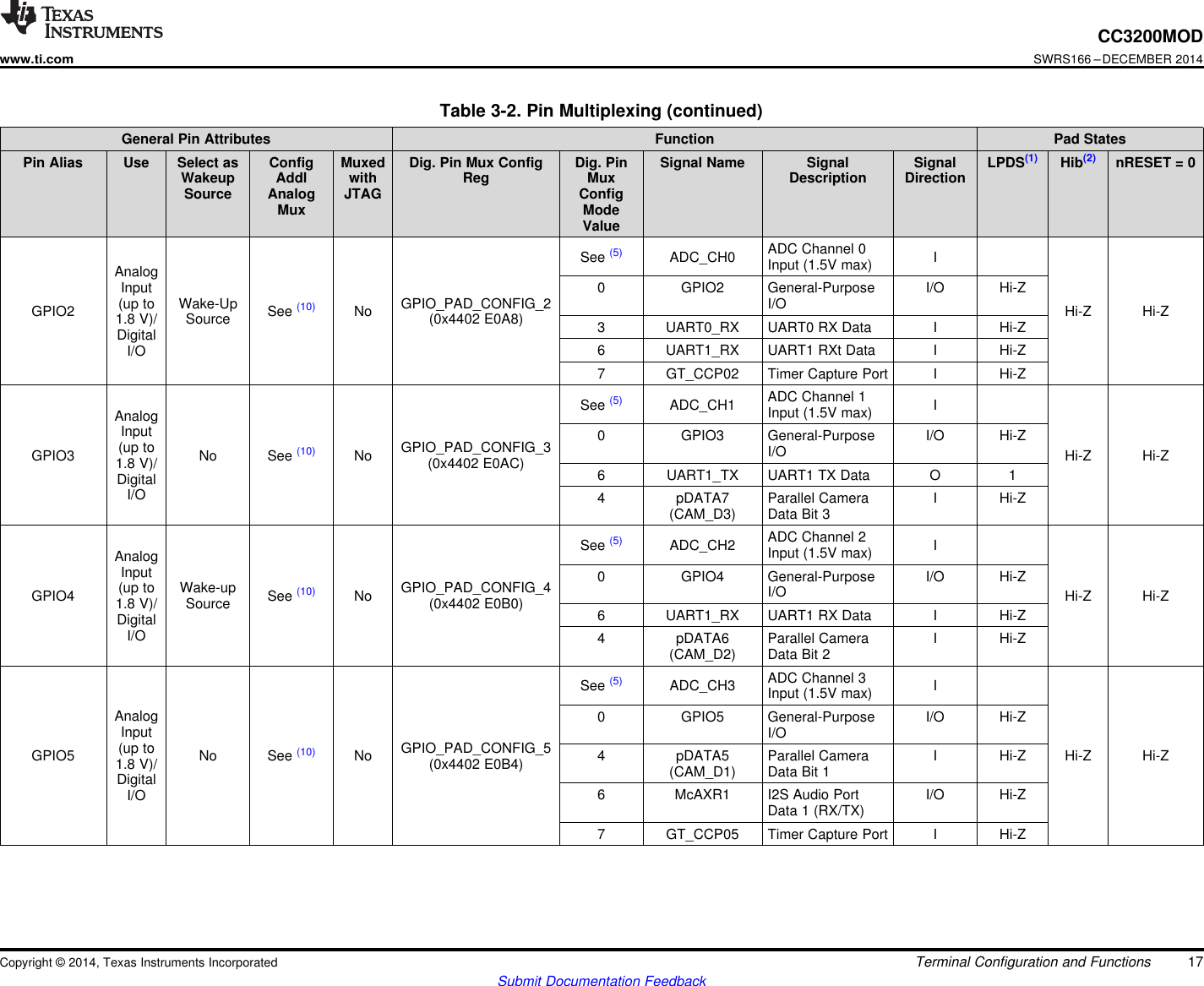

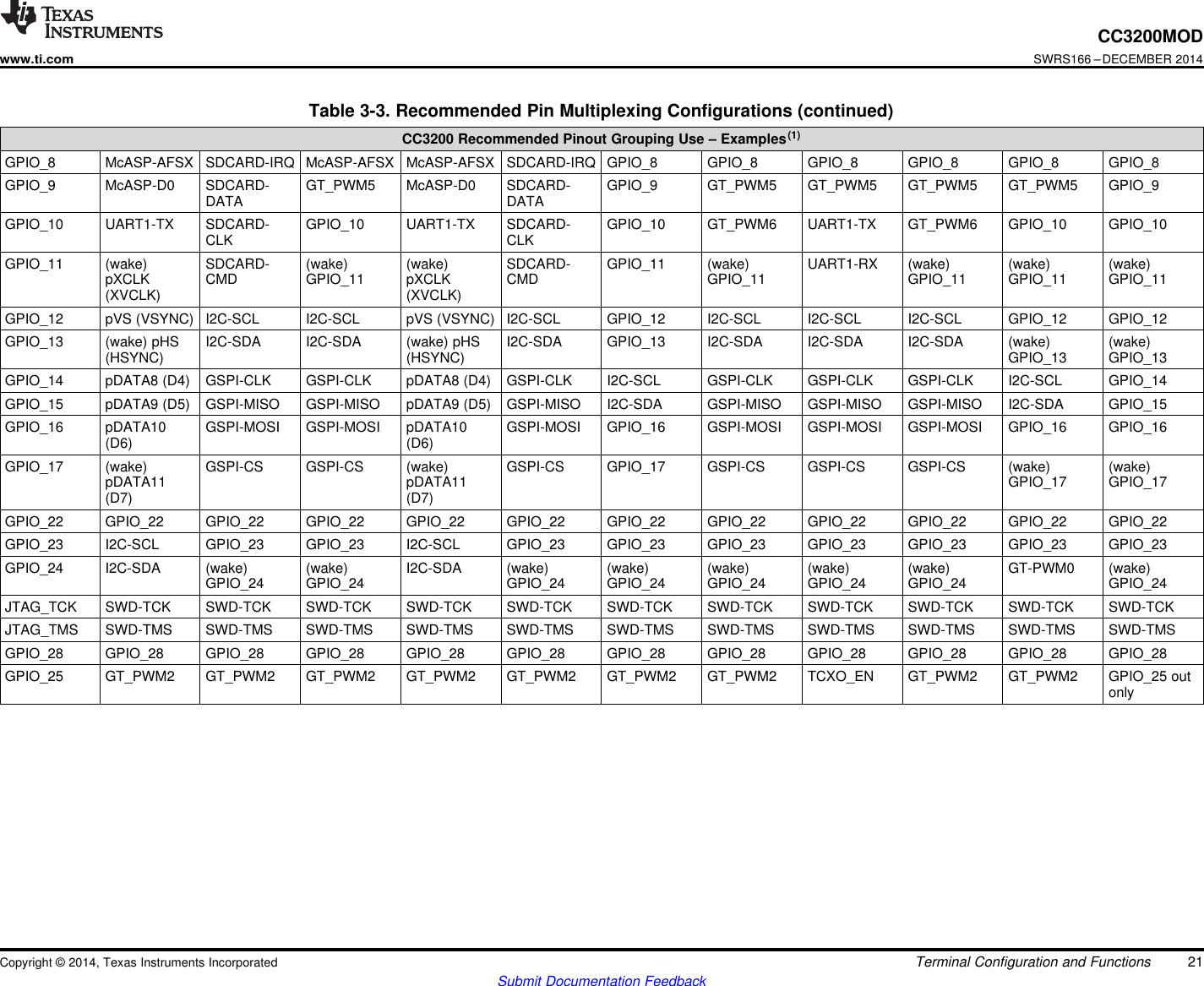

![CC3200MODSWRS166 –DECEMBER 2014www.ti.comPin Internal Pullup and Pulldown (25°C)(1)PARAMETER TEST CONDITIONS MIN NOM MAX UNITIOH Pullup current, VOH = 2.4 5 10 µA(VDD = 3.0 V)IOL Pulldown current, VOL = 0.4 5 µA(VDD = 3.0 V)(1) TI recommends using the lowest possible drive strength that is adequate for the applications. This recommendation minimizes the risk ofinterference to WLAN radio and mitigates any potential degradation of RF sensitivity and performance. The default drive-strength settingis 6 mA.4.7 Thermal Resistance Characteristics for MOB PackageNAME DESCRIPTION °C/W(1) (2) AIR FLOW (m/s)(3)RΘJC Junction-to-case 9.08 0.00RΘJB Junction-to-board 10.34 0.00RΘJA Junction-to-free air 11.60 0.00RΘJMA Junction-to-moving air 5.05 < 1.00PsiJT Junction-to-package top 9.08 0.00PsiJB Junction-to-board 10.19 0.00(1) °C/W = degrees Celsius per watt.(2) These values are based on a JEDEC-defined 2S2P system (with the exception of the Theta JC [RΘJC] value, which is based on aJEDEC-defined 1S0P system) and will change based on environment as well as application. For more information, see theseEIA/JEDEC standards:• JESD51-2, Integrated Circuits Thermal Test Method Environmental Conditions - Natural Convection (Still Air)• JESD51-3, Low Effective Thermal Conductivity Test Board for Leaded Surface Mount Packages• JESD51-7, High Effective Thermal Conductivity Test Board for Leaded Surface Mount Packages• JESD51-9, Test Boards for Area Array Surface Mount Package Thermal MeasurementsPower dissipation of 2 W and an ambient temperature of 70ºC is assumed.(3) m/s = meters per second.4.8 Reset RequirementPARAMETER SYMBOL MIN TYP MAX UNITOperation mode level ViH 0.65 × VBAT VShutdown mode level(1) ViL 0 0.6 V VMinimum time for nReset low for resetting the 5 msmoduleRise/fall times Tr/Tf 20 µs(1) The nRESET pin must be held below 0.6 V for the module to register a reset.26 Specifications Copyright © 2014, Texas Instruments IncorporatedSubmit Documentation Feedback](https://usermanual.wiki/Radiance-Instruments/TMW017G.TMW017G-WIFI-MODULE-SPECIFICATION/User-Guide-3512429-Page-26.png)

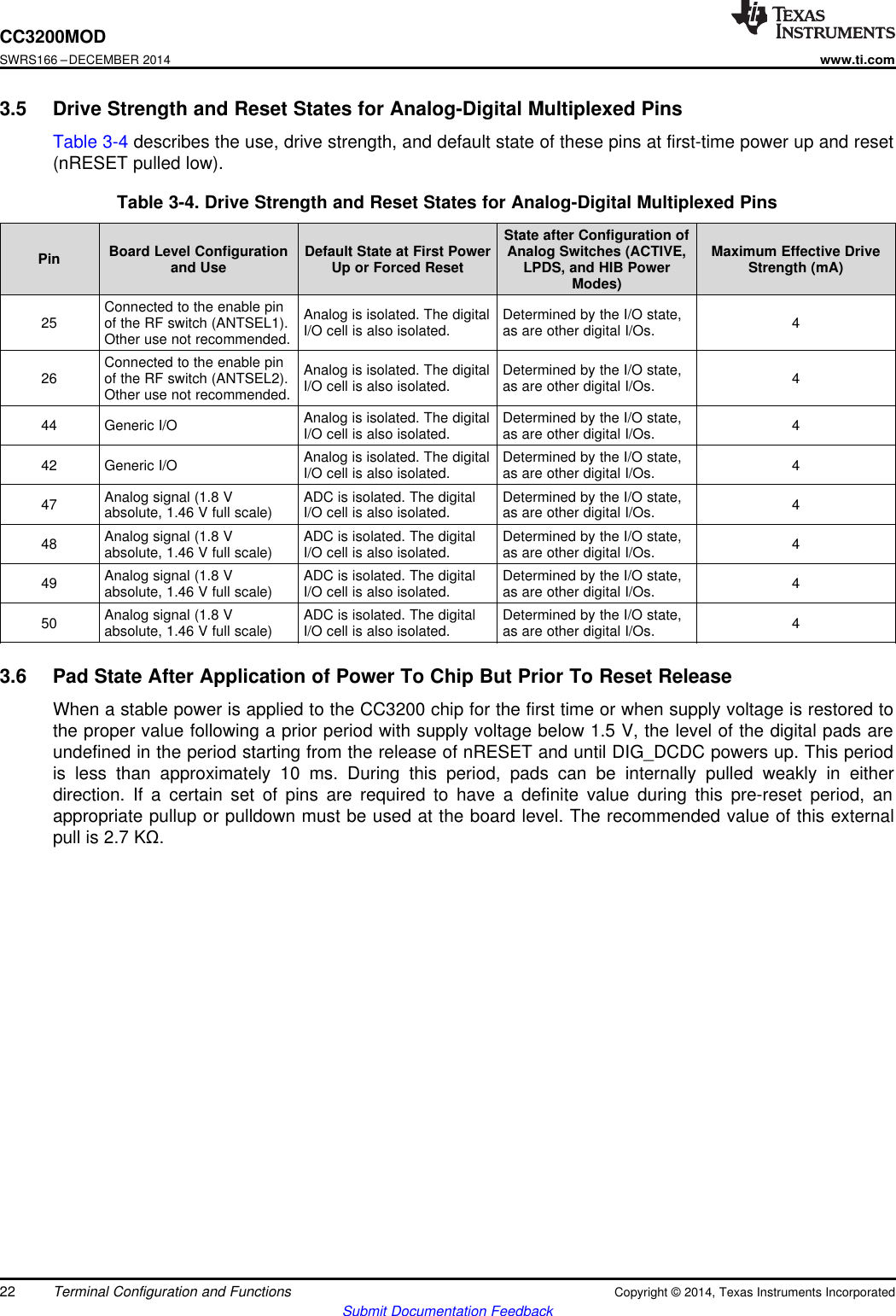

![CC3200MODSWRS166 –DECEMBER 2014www.ti.comSoP values are sensed from the device pin during power up. This encoding determines the boot flow.Before the device is taken out of reset, the SoP values are copied to a register and then determine thedevice opeartion mode while powering up. These values determine the boot flow as well as the defaultmapping for some of the pins (JTAG, SWD, UART0) Table 5-6 show the pull configurations.Table 5-6. CC32x0 Functional ConfigurationsNAME SoP[2] SoP[1] SoP[0] SoP MODE COMMENTUARTLOAD Pullup Pulldown Pulldown LDfrUART Factory/Lab Flash/SRAM load through UART.Device waits indefinitely for UART to load code.The SOP bits then must be toggled to configurethe device in functional mode. Also puts JTAG in4-wire mode.FUNCTIONAL_ Pulldown Pulldown Pullup Fn2WJ Functional development mode. In this mode, two-2WJ pin SWD is available to the developer. TMS andTCK are available for debugger connection.FUNCTIONAL_ Pulldown Pulldown Pulldown Fn4WJ Functional development mode. In this mode, four-4WJ pin JTAG is available to the developer. TDI, TMS,TCK, and TDO are available for debuggerconnection.The recommended value of pull resistors for SOP0 and SOP1 is 100 kΩand 2.7 kΩfor SOP2. SOP2 canbe used by the application for other functions after chip power-up is complete. However, to avoid spuriousSOP values from being sensed at power-up, TI strongly recommends that the SOP2 pin be used only foroutput signals. On the other hand, the SOP0 and SOP1 pins are multiplexed with WLAN analog test pinsand are not available for other functions.50 Detailed Description Copyright © 2014, Texas Instruments IncorporatedSubmit Documentation Feedback](https://usermanual.wiki/Radiance-Instruments/TMW017G.TMW017G-WIFI-MODULE-SPECIFICATION/User-Guide-3512429-Page-50.png)